プロセッサ(全68問中19問目)

広告

解説

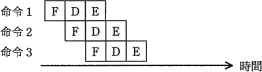

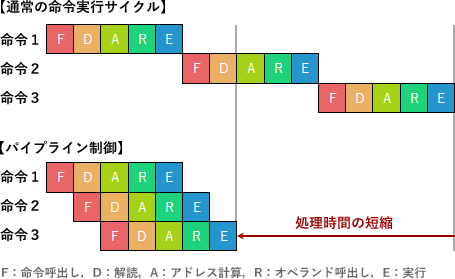

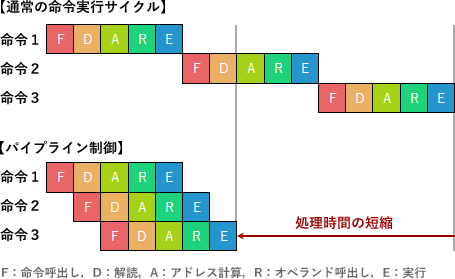

パイプライン制御は、CPUで処理される1命令を、命令読出し(フェッチ)、解読(デコード)、アドレス計算、オペランド呼出し、実行 というような複数のステージに分け、各ステージを少しずつずらしながら独立した処理機構で並列に実行することで、処理時間全体を短縮させる技法です。

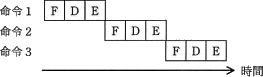

通常(非パイプライン)の流れでは、読出し→解読→実行という一連の処理が終了してから次の命令処理に移るというサイクルを繰り返しますが、パイプライン制御では命令処理の完了を待つことなく次の命令の処理に移れるためスループットが向上します。

通常(非パイプライン)の流れでは、読出し→解読→実行という一連の処理が終了してから次の命令処理に移るというサイクルを繰り返しますが、パイプライン制御では命令処理の完了を待つことなく次の命令の処理に移れるためスループットが向上します。

- 通常の逐次処理を表す図です。

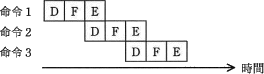

- 命令解読が行われるのは命令フェッチの後です。図ではFの前にDが入っているので処理順が不適切です。

- 正しい。各ステージが並列で実行されているのでパイプラインを最も適切に表した図です。

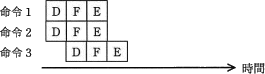

- 命令解読が行われるのは命令フェッチの後です。図ではFの前にDが入っているので処理順が不適切です。またパイプライン制御では、同じステージの処理を同じ時間には行えないので誤りです。

広告