平成24年春期試験問題 午前問24

問24解説へ

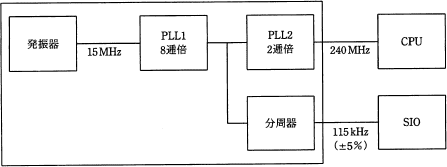

ワンチップマイコンにおける内部クロック発生器のブロック図を示す。15MHzの発振器と,内部のPLL1,PLL2及び分周器の組合せでCPUに240MHz,シリアル通信(SIO)に115kHzのクロック信号を供給する場合の分周器の値は幾らか。ここで,シリアル通信のクロック精度は±5%以内に収まればよいものとする。

- 1/24

- 1/26

- 1/28

- 1/210

広告

解説

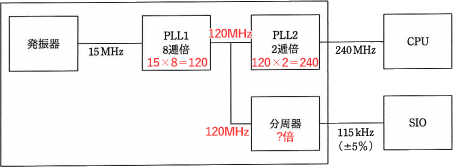

発振器から出力された15MHzは、PLL1で8倍にされて120MHzになります。その後PLL2でさらに2倍されて240MHzのクロック信号がCPUに届けられます。 問題の分周器の値ですが、分周器への入力が120MHz、SIO(シリアル通信)に供給されるクロック信号は115kHzなので、およそ1/1000の値になっていることに気が付きます。

問題の分周器の値ですが、分周器への入力が120MHz、SIO(シリアル通信)に供給されるクロック信号は115kHzなので、およそ1/1000の値になっていることに気が付きます。

120×106÷(115×103)≒103

よって、分周器の値は約1/1000に設定すればよいことになります。1000を2の累乗で表すと最も近いのが「1024=210」ですから、答えは1/210となります。

120×106÷(115×103)≒103

よって、分周器の値は約1/1000に設定すればよいことになります。1000を2の累乗で表すと最も近いのが「1024=210」ですから、答えは1/210となります。

広告